# Diplomarbeit

# Effiziente Unterstützung von Multiprozessorsystemen im Fiasco-Mikrokern unter Beachtung des zeitlichen Ausführungsverhaltens

Matthias Lange

26. September 2007

Technische Universität Dresden Fakultät Informatik Institut für Systemarchitektur Professur Betriebssysteme

Betreuender Hochschullehrer: Prof. Dr. rer. nat. Hermann Härtig

Betreuender Mitarbeiter: Dipl. Inf. Michael Peter

# Erklärung Hiermit erkläre ich, dass ich diese Arbeit selbstständig erstellt und keine anderen als die angegebenen Hilfsmittel benutzt habe. Dresden, den 26. September 2007 Matthias Lange

# **Danksagung**

Hiermit möchte ich meinem Betreuer Michael Peter für seine Unterstützung und Geduld bei der Anfertigung dieser Arbeit danken. Seine Hilfe bei den zahlreichen Debugging-Sessions und die anregenden Diskussionen sowie seine Kritik haben entscheidend zum Gelingen dieser Arbeit beigetragen.

Danken möchte ich hiermit auch Fabrice Bellard, der mit der Entwicklung von Qemu ein für mich unverzichtbares Testwerkzeug geschaffen hat. An dieser Stelle gebührt Michael Peter zusätzlicher Dank, denn durch dessen Erweiterung von Qemu ist es praktisch zum "Schweizer Taschenmesser" beim Debugging geworden.

Ebenfalls danken möchte ich Neal Walfield, dessen hartnäckige Fragen geholfen haben, manchen Sachverhalt klarer und deutlicher zu formulieren. Seine Hinweise haben dazu beigetragen, diese Arbeit in den richtigen Kontext zu rücken.

Meinem Vater möchte ich für das Korrekturlesen danken. Seine Anmerkungen haben geholfen, zahlreiche Abschnitte dieser Arbeit verständlicher und klarer zu formulieren.

# **Inhaltsverzeichnis**

| 1 | Einl | eitung                                          | 9  |

|---|------|-------------------------------------------------|----|

|   | 1.1  | Über diese Arbeit                               | 10 |

|   | 1.2  | Bezeichnungen                                   | 11 |

| 2 | Gru  | ndlagen und verwandte Arbeiten                  | 13 |

|   | 2.1  | L4-Mikrokerne                                   | 13 |

|   |      | 2.1.1 Fiasco                                    | 14 |

|   | 2.2  | Verwandte Arbeiten                              | 15 |

|   |      | 2.2.1 Linux-MP                                  | 15 |

|   |      | 2.2.2 RTLinux-MP                                | 16 |

|   |      | 2.2.3 K42                                       | 16 |

|   | 2.3  | MP-Erweiterungen für die L4-Schnittstelle       | 17 |

|   |      | 2.3.1 Skalierbare Mikrokernsysteme              | 17 |

|   |      | 2.3.2 Fiasco-SMP                                | 17 |

|   |      | 2.3.3 Aktuelle FIASCOMP-Variante                | 17 |

| 3 | Ana  | ılyse                                           | 21 |

|   | 3.1  | Modell 1 - Cross-Prozessor-Tasks                | 22 |

|   |      | 3.1.1 Scheduling                                | 23 |

|   |      | 3.1.2 Speicherverwaltung                        | 23 |

|   |      | 3.1.3 Prozessor-ID                              | 24 |

|   |      | 3.1.4 Kommunikation                             | 24 |

|   | 3.2  | Modell 2 - Gemeinsam genutzte Mapping-Datenbank | 24 |

|   |      | 3.2.1 Speicherverwaltung                        | 25 |

|   | 3.3  | Modell 3 - Thread-Migration                     | 27 |

|   |      | 3.3.1 Migration                                 | 28 |

|   |      | 3.3.2 Kommunikation                             | 28 |

|   | 3.4  | Diskussion                                      | 28 |

|   | _    | 3.4.1 Modelleigenschaften                       | 29 |

|   |      | 3.4.2 Vor- und Nachteile                        | 29 |

|   |      | 3.4.3 Schlussfolgerung                          | 30 |

| 4 | Des  | ign                                             | 31 |

| • | 4.1  | <del>-</del>                                    | 31 |

|   |      | 4.1.1 IPC                                       | 31 |

|   |      | 4.1.9 Deposite For Depos                        | 01 |

# In halts verzeichn is

| Gi     | USSar             |                                                                                                                                                     | 73                         |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 8<br>8 | Anh<br>ossar      | ang                                                                                                                                                 | 63<br>75                   |

| •      | 7.2               | Ausblick                                                                                                                                            | 60                         |

| 7      | <b>Z</b> usa 7.1  | ammenfassung und Ausblick Zusammenfassung                                                                                                           | <b>59</b>                  |

|        | 6.2               | 6.1.1 Parallele Nutzung mehrerer Prozessoren 6.1.2 Dynamische Arbeitslast 6.1.3 Lokale-IPC-Geschwindigkeit Echzeiteigenschaften 6.2.1 Mess-Szenario | 49<br>51<br>53<br>54<br>55 |

| 6      | <b>Eval</b> 6.1   | luierung<br>Funktionalität                                                                                                                          | <b>47</b>                  |

|        | 5.8<br>5.9        | MP-Preemption-Lock                                                                                                                                  | 44<br>45                   |

|        | 5.7               | Taskerzeugung                                                                                                                                       | 43<br>44                   |

|        | 5.5<br>5.6        | Allokatoren                                                                                                                                         | 43<br>43                   |

|        | 5.2<br>5.3<br>5.4 | 5.1.2 IPC-FensterStartvorgangTLB-KonsistenzAssistenten-Thread                                                                                       | 41<br>42<br>42<br>42       |

| 5      | <b>Imp</b> 5.1    | lementierung         Prozessorlokale Daten                                                                                                          | <b>41</b><br>41<br>41      |

|        | 4.2               | 4.2.1 Algorithmus                                                                                                                                   | 33<br>37                   |

|        | 4.2               | 4.1.3 Nachrichtenrate                                                                                                                               | $\frac{31}{32}$            |

# 1 Einleitung

In den letzten Jahren sind Mehrkernprozessor- und Multiprozessorsysteme ein allgemeiner Trend in der Halbleiterindustrie geworden. Es wird erwartet, dass in den nächsten Jahren Prozessoren auf den Markt kommen, die mit Dutzenden oder sogar Hunderten Kernen ausgestattet sind (siehe [ea05]). Der Grund ist, dass Taktratensteigerungen von Prozessoren allein nicht mehr zu den gewünschten Leistungssteigerungen führen. Zusätzlich führen hohe Taktraten zu hohen Verlustleistungen. Multiprozessorsysteme werden in der Regel niedriger getaktet und versuchen Taskparallelität besser auszunutzen. Um die Leistungsfähigkeit dieser Architekturen vollständig zu erschließen, müssen Betriebssysteme und Anwendungsprogramme daran angepasst werden.

Ein Mikrokern ist ein minimaler Betriebssystemkern. Er stellt grundlegende Primitive für die Konstruktion von Betriebssystemen zur Verfügung. Gegenüber monolithischen Systemen bieten Mikrokerne eine zuverlässige Basis für den Aufbau komplexer Systeme, da Komponenten, für die kein Wohlverhalten garantiert werden kann, voneinander isoliert sind. Mikrokerne der ersten Generation litten unter Geschwindigkeitsproblemen, die bei der Entwicklung von Mikrokernen der zweiten Generation gezielt gelöst wurden. L4 ist ein Mikrokern der zweiten Generation und bezeichnet sowohl eine Schnittstelle als auch eine Implementierung. Der an der TU Dresden entwickelte Mikrokern FIASCO ist eine echtzeifähige Implementierung der L4-Schnittstelle. Seine Architektur erlaubt es neben Nicht-Echtzeitaufgaben auch Echtzeitaufgaben zu bearbeiten. Trotzdem können für Echtzeitaufgaben Garantien für die Einhaltung von Bearbeitungsfristen gegeben werden. Echtzeitaufgaben, aber auch allgemeine Arbeitslasten wie z.B. Compiler, können von SMP-Systemen profitieren. Deshalb ist eine Unterstützung von Multiprozessorsystemen im FIASCO-Mikrokern wünschenswert.

Die bisher existierende Unterstützung von FIASCO für Mehrprozessorsysteme stellt hohe Ressourcenanforderungen und leidet unter Leistungsdefiziten bei Anwendungen, die auf mehr als einem Prozessor laufen. Ziel der FIASCOMP-Implementierung war es, mit Hilfe eines einfachen Kern-Modells Multiprozessorhardware für FIASCO nutzbar zu machen und die Echtzeiteigenschaften der Uniprozessorvariante zu erhalten. Die aktuelle FIASCOMP-Variante hat einige Limitierungen. Threads einer Task können nur auf einem Prozessor laufen und Speicher-Mappings nicht über Prozessorgrenzen hinweg vergeben werden. Das Modell hat bei der Implementierung von gemeinsam genutztem Speicher einen hohen Ressourcenbedarf. In dieser Diplomarbeit werde ich Möglichkeiten untersuchen, wie FIASCOMP weiterentwickelt werden kann, um derartige Beschränkungen zu beseitigen. Die vorgeschlagenen Lösungen werden bewertet und anhand einer prototypischen Implementierung wird die Eignung zum Erreichen der Ziele untersucht.

Um Ineffizienzen der aktuellen Implementierung zu beseitigen, wird auf Kern-Ebene ein gemeinsam genutzter Adressraum implementiert. *Threads* einer Task können auf un-

terschiedlichen Prozessoren laufen. Der Zugriff auf globale Datenstrukturen muss mit Hilfe eines echtzeitkompatiblen Synchronisationsmechanismus synchronisiert werden. Der Ex-Regs-Systemruf muss erweitert werden, damit die Erzeugung von Threads auf anderen Prozessoren möglich ist. Seitenfehlernachrichten über Prozessorgrenzen hinweg werden erlaubt. Ein Konsistenzprotokoll stellt die Konsistenz der Translation Lookaside Buffer (TLBs) der einzelnen Prozessoren mit den Seitentabellen der Tasks sicher.

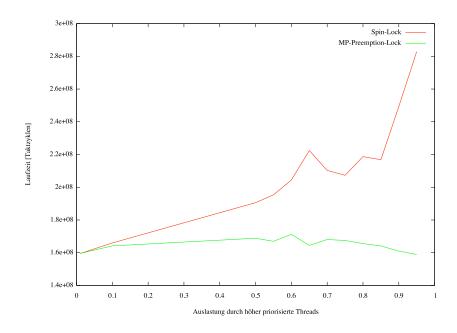

Die Mapping-Datenbank ist eine gemeinsam genutzte Ressource und deshalb muss der Zugriff darauf synchronisiert werden. Die Synchronisation hat Auswirkungen auf das Ausführungsverhalten des Gesamtsystems. Die Synchronisation mit Hilfe eines nicht-unterbrechbaren Spin-Locks umzusetzen, brachte Probleme mit dem Zeitverhalten für Echtzeitaufgaben. Ein unterbrechbares Spin-Lock würde zwar das Zeitverhalten verbessern, allerdings gibt es mit einem solchen Mechanismus Probleme mit der Fairness, denn *Threads* können verhungern. Deshalb wird ein unterbrechbarer Lock-Mechanismus benötigt, der das Zeitverhalten nicht negativ beeinflusst und der keine Fairness-Probleme hat.

Im bisherigen FIASCO-Kern werden zum Schutz von einigen kritischen Abschnitten Helping-Locks (siehe [Hoh02]) verwendet. Bei Helping-Locks ist der Lock-Halter unterbrechbar, und unbegrenzte Prioritätsinversion wird vermieden. Helping-Locks funktionieren im Cross-Prozessor-Fall nicht mehr, da das direkte Umschalten zum Lock-Halter im Multiprozessorfall nicht mehr möglich ist. Ein potentieller Helfer kann nicht direkt zum Lock-Halter umschalten, da im Multiprozessorfall nicht sichergestellt ist, dass der Lock-Halter nicht gerade selbst aktiv ist. In dieser Arbeit stelle ich einen Helping-Mechanismus vor, der auch im Cross-Prozessor-Fall anwendbar ist. Der Lock-Mechanismus ermöglicht die Unterbrechbarkeit des Lock-Halters und vermeidet das Threads, beim Versuch auf das Lock zuzugreifen, verhungern können. Unterbrechbarkeit ist notwendig, damit Echtzeitaufgaben erfüllt werden können. Mit dem MP-fähigen Helping-Mechanismus lässt sich eine systemglobale Mapping-Datenbank, die Grundlage für einen gemeinsamen Adressraum über Prozessorgrenzen hinweg, implementieren. Anhand einer Referenzimplementierung für den FIASCO-Mikrokern untersuche ich Eigenschaften dieses Locks und vergleiche sie mit denen anderer Lock-Varianten.

# 1.1 Über diese Arbeit

Diese Diplomarbeit beschäftigt sich mit der Weiterentwicklung der Multiprozessorvariante des FIASCO-Mikrokerns. Ziel ist es, Limitierungen der aktuellen Implementierung zu beseitigen und damit eine effizientere L<sup>4</sup>Linux-MP-Implementierung auf dem Multiprozessorkern zu ermöglichen.

Im folgenden Kapitel werde ich zunächst das Konzept von Mikrokernbetriebssystemen vorstellen und anschließend die L4-Schnittstelle erläutern. Die folgenden Abschnitte beschäftigen sich mit verwandten Arbeiten auf dem Gebiet der SMP-Betriebssysteme. Darin wird auch untersucht, inwiefern Echtzeiteigenschaften eine Rolle beim Design dieser Systeme gespielt haben. Am Ende des Kapitels stelle ich die aktuelle FIASCOMP-Implementierung vor und ich erläutere für diese Diplomarbeit relevante Eigenschaften

und Limitierungen dieser Implementierung.

Im Analyse-Kapitel stelle ich drei Modelle vor, nach denen FIASCOMP weiterentwickelt werden kann. Die Ziele dabei sind, den Ressourcen-Bedarf durch

- Vermeidung der Duplikation der Seitentabellen im Kern und

- eine dedizierte Mapping-Datenbank für jeden Prozessor

zu senken. Die in den drei im Analyse-Kapitel vorgestellten Modellen auftretenden Probleme bei der Erhaltung der Echtzeiteigenschaften von FIASCO und die Verzögerung von prozessorlokalen Operationen sollen vermieden werden. Das in diesem Kapitel vorgestellte Modell 2 ist ein symmetrisches Modell, d.h. alle Operationen sind auf allen Prozessoren möglich. Thread-Migration wird nicht durch den Kern unterstützt. Modell 2 implementiert auf Kern-Ebene einen gemeinsam genutzten Adressraum, indem bislang prozessorlokal definierte Datenstrukturen global definiert werden. Die im aktuellen FIASCOMP-Modell bislang dediziert für jeden Prozessor vorhandenen Mapping-Datenbanken werden durch eine systemglobale ersetzt.

Im Design-Kapitel beschäftige ich mich mit der Entwicklung eines echtzeitkompatiblen MP-Locking-Mechanismus. Dieser Mechanismus wird benötigt, um Zugriffe auf die systemglobale Mapping-Datenbank zu synchronisieren und dabei vorhersagbares Verhalten von Echtzeit-*Threads* zu ermöglichen.

Das Implementierungs-Kapitel beschreibt einige Aspekte der Implementierung des im Analyse-Kapitel vorgestellten Modells 2. Zunächst erläutere ich, welche Änderungen an der bestehenden Fiascomp-Implementierung notwendig waren. Den Abschluss bildet ein Abschnitt über die Umsetzung des MP-Preemption-Locks.

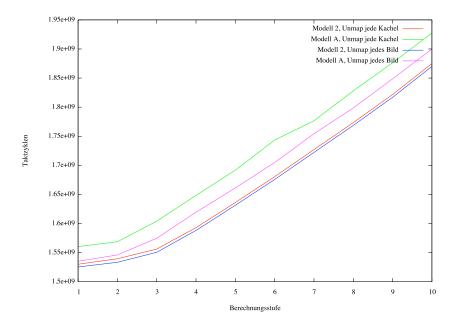

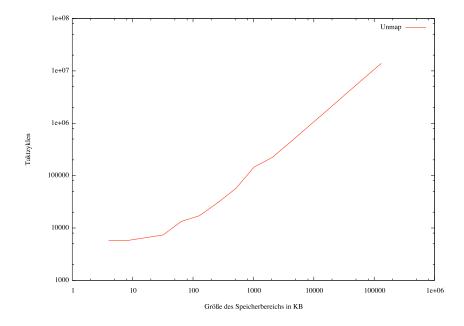

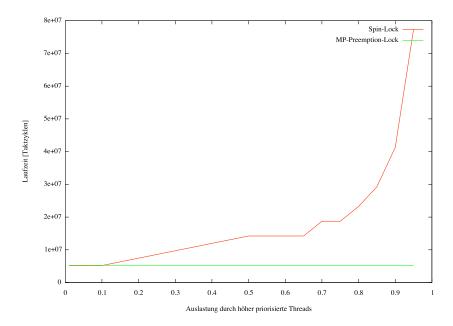

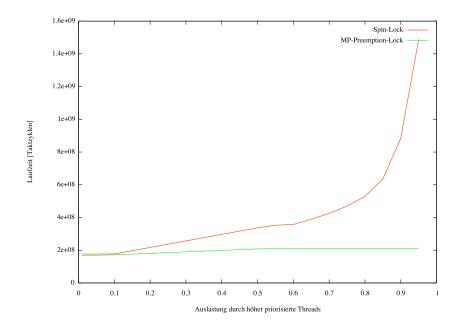

Im vorletzten Kapitel untersuche ich, wie gut die im Design-Kapitel genannten Ziele erreicht wurden. Es wird gezeigt, dass der Ressourcenverbrauch gegenüber der ursprünglichen Implementierung gesenkt werden konnte. Gleichzeitig wurde die Laufzeit lokaler Operationen erhalten. Weiterhin werde ich anhand unterschiedlicher Messungen und Kriterien zeigen, dass das MP-Preemption-Lock die Echtzeiteigenschaften des FIASCO-Mikrokerns erhält.

Den Abschluss dieser Arbeit bildet eine kurze Zusammenfassung. Anschließend gebe ich einen Ausblick darauf, welche zukünftigen Weiterentwicklung möglich sind.

#### 1.2 Bezeichnungen

Die Informatik ist stark durch englische Begriffe und Bezeichnungen geprägt. Ich habe mich bemüht, soweit wie möglich passende deutsche Entsprechungen dafür zu finden. Für manche Begriffe lassen sich jedoch keine vernünftigen Entsprechungen finden. Um in dieser Diplomarbeit einen schwer verständlichen "Denglisch-Stil" zu vermeiden, werden solche Begriffe von mir in kursiver Schrift hervorgehoben, zum Beispiel *Idle-Thread*. Quelltexte werden in Schreibmaschinenschrift geschrieben, zum Beispiel \_\_main.

# 1 Einleitung

# 2 Grundlagen und verwandte Arbeiten

Im ersten Abschnitt dieses Kapitels stelle ich das Konzept von Mikrokernbetriebssystemen vor und erläutere die Eigenschaften der FIASCO-Schnittstelle. Anschließend stelle ich Arbeiten vor, die sich mit SMP-Betriebssystemen beschäftigen. Im zweiten Teil beschreibe ich für meine Arbeit wichtige Aspekte des aktuellen FIASCO-Multiprozessorkerns. Im letzten Teil stelle ich Mechanismen vor, die für die Konstruktion von SMP-Betriebssystemen wichtig sind.

#### 2.1 L4-Mikrokerne

Ein Mikrokern ist ein minimaler Betriebssystemkern. Er stellt grundlegende Primitive wie z.B. Adressräume, *Threads* und Inter-Prozesskommunikation (im folgenden IPC genannt) zur Verfügung. Mit Hilfe dieser Primitive werden Betriebssystemdienste, zum Beispiel Gerätetreiber und Dateisysteme, außerhalb des Kerns implementiert (siehe [Lie95]).

Im Vergleich zu monolithischen Betriebssystemkernen ergibt sich eine höhere Stabilität gegenüber Fehlfunktionen einzelner Komponenten, da diese bei Mikrokernsystemen voneinander isoliert sind. Systeme mit hohen Sicherheitsanforderungen profitieren von der kleineren Codebasis von Mikrokernen, da diese leichter zu überprüfen ist.

In unterschiedlichen Varianten wurde in der Vergangenheit bereits versucht, die Idee der Mikrokernsysteme in die Praxis umzusetzten. Das bekannstete Projekt dürfte hier das Mach-Projekt der Carnegie Mellon University [BBB+90] sein. Solche Projekte führten zunächst zu keinen Erfolgen, da die Ausführungsgeschwindigkeit dieser Systeme im Vergleich zu klassischen monolithischen Systemen zu gering war [Raw97]. Dafür verantwortlich waren unterschiedliche Designschwächen, hauptsächlich mangelnde IPC-Geschwindigkeit und *Double-Paging*. Derartige Mikrokerne werden als Mikrokerne der ersten Generation bezeichnet.

Jochen Liedtke entwickelte mit L4 einen Mikrokern der zweiten Generation, wobei L4 sowohl die erste Implementierung als auch eine Schnittstellendefinition bezeichnet. Mit den von ihm in [Lie96] beschriebenen Mechanismen (Adressräume, *Threads* und IPC) wurde versucht, die Geschwindigkeitsprobleme zu lösen. Die IPC-Kommunikation wurde grundlegend vereinfacht. Solche Kerne bieten einen sehr effizienten Weg für IPC. Sie verfügen weiterhin nur über drei Abstraktionen (*Threads*, Adressräume und IPC) und versuchen, sämtliche Strategien, zum Beispiel Seitenersetzungsalgorithmus, aus dem Kern zu entfernen. Der Vorteil dieses Designs ist, dass auf Benutzerebene implementierte Strategien von zusätzlichem Wissen über die Ausführungsumgebung profitieren können. Dieses Wissen ist nur schwer in einem Betriebssystemkern zu implementieren.

FIASCO ist ein an der TU Dresden entwickelter Mikrokern, der eine der L4-Schnittstellen implementiert. Bei der Entwicklung von FIASCO wurde viel Wert auf Echtzeitfähigkeiten gelegt, die sich in einem Kern-Design mit nur sehr kurzen, nicht unterbrechbaren Abschnitten und kurzen Interrupt-Latenzen wiederfinden. Der FIASCO-Mikrokern wurde in einer vereinfachten Variante der Programmiersprache C++ geschrieben. Es gibt Varianten für IA-32, AMD64 und ARM.

Weitere L4-Implementierungen sind:

- L4ka::Pistachio: Pistachio wird an der Universität Karlsruhe entwickelt und implementiert das L4v4-API für IA-32, IA-64, Alpha, AMD64, ARM, MIPS 64-bit, PowerPC 32-bit und PowerPC 64-bit. Er wird in eingebetteten Systemen, Standardsystemen und Multiprozessorsystemen eingesetzt. Ein wichtiges Ziel bei der Entwicklung von Pistachio ist Portabilität [Pis].

- **L4/MIPS:** Wird an der University of New South Wales entwickelt und läuft auf MIPS-Prozessoren (für Forschung und Lehre, wurde durch L4/Pistachio im Rahmen des L4/NICTA-Projekts abgelöst) (siehe [Hei01]). Die 64-bit-Variante diente als Basis für das SASOS-Projekt (Mungi)

- **OKL4:** Open Kernel Labs (für eingebette Systeme) (siehe [okl]), ist aus L4ka::Pistachio hervorgegangen

- **Sysgo P4** Sysgo wird für eingebette Systeme in der Automobilindustrie verwendet (siehe [sys]).

- **L4.sec** TU-Dresden, Erweiterung des L4-APIs um Mechanismen für Kommunikationskontrolle und Kern-Ressourcen-Management (siehe [Kau05])

#### 2.1.1 Fiasco

In den folgenden Abschnitten erläutere ich die L4-Schnittstelle.

#### Adressräume

Adressräume sind Schutzdomänen mit einer eindeutigen Bezeichnung (Adressraum-ID). Sie sind gegenseitig voneinander isoliert. Zugriffsrechte auf Ressourcen werden an Adressräume vergeben. Adressräume können eine bestimmte, feste Anzahl (bei FIASCO maximal 128) an *Threads* beinhalten.

Adressräume werden in L4-Systemen rekursiv aufgebaut. Ausgehend vom Wurzel-Adressraum ( $\sigma_0$ ) wird Speicher durch Map-Operationen (map und grant) weitergegeben bzw. durch die Unmap-Operation (unmap) wieder entzogen. Der  $\sigma_0$ -Server bekommt beim Systemstart vom Kern den physischen Speicher zugewiesen. Der Kern kann bestimmte Speicherregionen reservieren, die dann vom  $\sigma_0$ -Server nicht weitergegeben werden. Der physische Speicher wird bei  $\sigma_0$  gleich 1:1 (d.h. physische Adresse = virtuelle Adresse) eingeblendet.

#### **Threads**

Threads sind eine Prozessorabstraktion. Sie haben zwei Funktionen: sie bilden Endpunkte für die Kommunikation und bekommen vom Scheduler Rechenzeit für einen Prozessor zugewiesen.

Das Scheduling in FIASCO basiert auf statischen Prioritäten. *Threads* mit höherer Priorität verdrängen *Threads* mit niedrigeren Prioritäten. *Threads* mit gleichen Prioritäten werden nach dem *Round-Robin-*Verfahren eingeplant.

#### **IPC**

Zwischen *Threads* können über IPC Nachrichten ausgetauscht werden. Die Kommunikation ist bei L4 synchron und erfolgt über ein sog. Rendezvous von Sender und Empfänger. Nachrichten, die durch IPC übertragen werden, können einzelne Maschinenworte (Short-IPC), Speicher-Mappings und Puffer (Long-IPC) enthalten.

Seitenfehler werden auf IPC abgebildet. Der auslösende *Thread* wird blockiert und der Kern schickt im Namen dieses *Threads* eine Nachricht mit der Seitenfehleradresse an den Pager-Thread. Der *Pager-Thread* antwortet mit der Rücksendung eines Speicher-Mappings. Erst nach Empfang der Antwort kann der *Thread*, der den Seitenfehler ausgelöst hat, weiter laufen. Für den Empfang eines Speicher-Mappings muss der Empfänger ein sog. *Receive-Window* angeben. Das ist ein Bereich des Adressraums, in den das Speicher-Mapping eingefügt werden soll. Damit kann ein Empfänger vermeiden, dass Teile seines Adressraums durch manipulierte Speicher-Mappings verändert werden.

Für einen Thread gehört der Pager-Thread zur Trusted Computing Base, denn bei einem Seitenfehler wird der gesamte Adressraum als Receive-Window angegeben. Deshalb muss ein Thread seinem Pager-Thread vertrauen. Ein böswilliger Pager-Thread kann durch manipulierte Speicher-Mappings den Empfänger korrumpieren.

Durch Hardware oder Software ausgelöste Ausnahmen (im folgenden Interrupts) werden ebenfalls auf IPC-Nachrichten abgebildet. Dazu registriert sich ein *Thread* auf Benutzerebene für einen bestimmten Interrupt. Wird dieser Interrupt ausgelöst, so stellt der Kern eine entsprechende Nachricht an den registrierten *Thread* zu.

#### 2.2 Verwandte Arbeiten

In diesem Abschnitt stelle ich andere Arbeiten und Implementierungen zu symmetrischen Multiprozessorsystemen vor. Bei der Analyse dieser Arbeiten zeigt sich, dass verbreitete SMP-Betriebssysteme häufig einen gemeinsam genutzten Adressraum anbieten.

#### 2.2.1 Linux-MP

Linux unterstützt SMP-Systeme auf einer Vielzahl von Plattformen. Eine zentrale Linux-Abstraktion ist der Prozess. Ein Prozess ist ein Programm in Ausführung. Einem Prozess werden durch das Betriebssystem Ressourcen (Betriebsmittel und Rechenzeit) zugewiesen. *Threads* sind in Linux leichtgewichtige Prozesse, die sich Ressourcen mit dem Vater-

Prozess teilen können. Der Kern implementiert für Prozesse einen auf allen Prozessoren gemeinsam nutzbaren Adressraum. Prozesse benötigen kein Wissen über die darunterliegende Architektur, um z.B. von der parallelen Ausführung unterschiedlicher *Threads* zu profitieren. Der Kern organisiert selbstständig eine Lastverteilung. In [BH03] beschreibt Ray Bryant, wie u.a. durch Integration eines O(1)-Schedulers und die Ersetzung des *Big-Kernel*-Locks durch eine feingranularere Variante die Skalierbarkeit des Linux-Kerns auf bis zu 64 Prozessoren verbessert werden konnte. Auf einem Intel-Itanium-System mit 64 Prozessoren konnte damit ein fast linearer Geschwindigkeitszuwachs erzielt werden.

In der Veröffentlichung von Bryant wird gezeigt, dass die globale Runqueue im Linux-Kern 2.4 (und früher) einen Flaschenhals darstellt. Deshalb wird in Linux ein Scheduler verwendet, der mit prozessorlokalen Warteschlangen arbeitet. Die Lastverteilung wird durch einen periodisch laufenden Prozess realisiert, der lauffähige Threads anhand bestimmter Kriterien auf weniger ausgelastete Prozessoren migriert. Diese Kriterien sind nicht trivial und können große Auswirkungen auf die Gesamtgeschwindigkeit haben. So werden z.B. Threads mit warmen Caches nicht zur Migration ausgewählt.

Linux-MP ist ein SMP-Betriebssystemkern für eine allgemeine Arbeitslast des Systems. Echtzeitfähigkeiten spielen bei der Entwicklung nur eine untergeordnete Rolle.

#### 2.2.2 RTLinux-MP

RTLinux [YB] eine Erweiterung des Linux-Kerns, die mit dem POSIX 1003.13 Standard kompatibel ist. RTLinux ist ein echtzeitfähiger Betriebssystemkern. Auf diesem Betriebssystemkern wird parallel zu Echtzeitanwendungen ein Standard-Linux-System ausgeführt. RTLinux unterstützt SMP auf PowerPC-Prozessoren. Echtzeit-*Threads* lassen sich bestimmten Prozessoren zuordnen. Ein "Prozessor-Reservierungs-Schema" erlaubt es, bestimmte Prozessoren eines SMP-Systems für Echtzeitaufgaben zu reservieren. Damit werden Störungen durch die Ausführung von Nicht-Echtzeitanwendungen vermieden. Das Scheduling erfolgt prozessorlokal.

Die Zukunft von RTLinux ist unklar, da momentan keine Weiterentwicklung stattfindet. Dennoch ist das Design des Systems interessant, denn für FIASCOMP wird eine ähnliche Arbeitslast, bestehend aus Echtzeitaufgaben und parallel dazu ein L<sup>4</sup>Linux-MP, angenommen. RTLinux bietet allerdings keinen Adressraumschutz für Echtzeit-Tasks.

#### 2.2.3 K42

K42 [ea06] ist ein Betriebssystem von IBM für Multiprozessorsysteme. Es ist ein Forschungsprojekt mit dem Ziel, sowohl kleine als auch große Multiprozessorsysteme zu unterstützen. Es basiert auf einem Mikrokern und zielt auf Geschwindigkeit und Skalierbarkeit auf bis zu mehreren hundert Prozessoren ab. K42 unterstützt das Linux-API und -ABI, so dass Linux-Anwendungen ohne Anpassung auf diesem Betriebssystem ausgeführt werden können. Echtzeitfähigkeiten waren ursprünglich nicht Bestandteil des Systemdesigns.

# 2.3 MP-Erweiterungen für die L4-Schnittstelle

In [Völ02] schlägt Völp ein Multiprozessormodel für das L4v2-API vor. Die Kernschnittstelle bleibt dabei mit der Uniprozessorvariante kompatibel, so dass unmodifizierte Anwendungen weiter ausgeführt werden können. Weitere Ziele waren Flexibilität, Geschwindigkeit, Transparenz für unmodifizierte und Nicht-Transparenz für an SMP angepasste Anwendungen.

Der Scheduler arbeitet prozessorlokal und deshalb haben Prioritäten auch nur eine lokale Bedeutung.

Dieser Ansatz geht von einer allgemeinen Arbeitslast des Systems aus.

#### 2.3.1 Skalierbare Mikrokernsysteme

In [Uhl05] beschreibt Uhlig einen komplexen Synchronisationsmechanismus für Mikrokerne, der Geschwindigkeit und Skalierbarkeit des Systems erhält. Dazu schlägt er eine dynamische Anpassung der Synchronisationstrategie und -granularität vor.

Er beschreibt einen Mechanismus zur Anpassung der Synchronisationsmethode zur Laufzeit, der *adaptive locks* genannt wird. Locks können prozessorlokal oder prozessorübergreifend sein. Anwendungen müssen dem Kern durch Hinweise mitteilen, welches Schema benutzt werden soll. Das erfordert, dass die Anwendungen die darunter liegende Architektur kennen müssen, um sie nutzen zu können.

Die Arbeit beschreibt ein allgemeines Modell für eine allgemeine Arbeitslast des Systems. Uhligs Ziel war es, dass alle Anwendungen, wenn auch mit möglichen Geschwindigkeitsverlusten, lauffähig bleiben. Echtzeitfähigkeiten waren nicht Ziel der Arbeit.

#### 2.3.2 Fiasco-SMP

Michael Peter beschreibt in [Pet01] einen ersten Ansatz, den FIASCO-Mikrokern für SMP-Systeme anzupassen. Da der Kern bereits voll unterbrechbar war, wurde es als ausreichend erachtet, die Lock-Infrastruktur für Multiprozessorsysteme anzupassen. Locks haben im SMP-Fall unterschiedliche Aufgaben, die sie im Uniprozessorfall nicht haben. Eine einfache Verallgemeinerung der Lock-Semantik ist daher nicht möglich. Das von Peter entwickelte Design bedingte einen hohen Mehraufwand für lokale Operationen und wurde bei Weiterentwicklungen von FIASCO in den folgenden Jahren nicht weiter angepasst.

#### 2.3.3 Aktuelle FiascoMP-Variante

In [Sch06] stellt Sven Schneider einen alternativen Ansatz vor. Ziel dieser Implementierung war es, ein Modell zu realisieren, welches:

- die Echtzeiteigenschaften des Fiasco-Mikrokerns erhält,

- das genug Funktionalität bietet, um darauf L<sup>4</sup>Linux auf mehreren Prozessoren auszuführen und

• möglichst wenig Änderungen am Kern verlangt.

Es wurde ein System realisiert, welches auf jedem Prozessor eine Instanz von FIAS-CO ausführt. Nachrichten können mit Hilfe eines Message-Passing-Systems sehr effizient zwischen einzelnen Instanzen ausgetauscht werden. Andere Interaktionen sind nicht möglich.

#### Kommunikation

Für die Cross-Prozessor-Kommunikation wird ein *Message-Box-System* verwendet. Es wurde im Hinblick darauf entwickelt, dass eine Vielzahl an Operationen weiterhin prozessorlokal und damit schnell erfolgen können. Daher ist es nicht wünschenswert, alle Operationen, die parallel von Prozessoren durchgeführt werden können, mit einem teuren Synchronisationsmechanismus zu schützen.

Jeder Prozessor darf zu jedem Zeitpunkt nur eine ausstehende Nachricht haben. Während er auf die Bearbeitung seiner verschickten Nachricht wartet, muss er evtl. einkommende Nachrichten bearbeiten. Damit werden Blockierungen vermieden.

Nachrichten haben einen bestimmten Nachrichtentyp, anhand dessen die richtige Funktion für die Bearbeitung der Nachricht ausgewählt wird. *Threads* kommunizieren bei FIASCO mittels Inter-Prozess-Kommunikation (IPC). In der aktuellen Implementierung steht *Threads* für die Kommunikation über Prozessorgrenzen hinweg nur *Short*-IPC zur Verfügung. Der *Long*-IPC-Mechanismus ist prinzipiell möglich, wurde aber bislang nicht implementiert. Speicher-Mappings können nicht über Prozessorgrenzen hinweg verschickt werden.

#### Mapping-Datenbank

Fiasco unterstützt die Möglichkeit, Adressräume rekursiv aufzubauen (siehe [Lie96]). Die hierarchischen Abhängigkeiten von eingeblendeten Seiten werden in der Mapping-Datenbank gespeichert. Das ist nötig, damit eine Seite später aus jenen Adressräumen, denen die selbe Seite eingeblendet ist, wieder entfernt werden kann.

Jeder Prozessor verwaltet eine eigene Mapping-Datenbank für die bei ihm laufenden Tasks. Per Konstruktion sind keine Cross-Prozessor-Mappings erlaubt. Ein gemeinsam genutzter Adressraum muss daher auf Benutzerebene durch kooperierende Tasks konstruiert werden.

#### Limitierungen

Das bislang implementierte Modell hat einige Limitierungen:

**Tasks:** Threads einer Task können nur auf einem Prozessor ausgeführt werden. Dieser wird bei der Task-Erzeugung festgelegt und kann später nicht geändert werden.

**Mappings:** Das Modell erlaubte keine Mappings über Prozessorgrenzen hinweg.

Aus diesen Limitierungen ergibt sich bei der Konstruktion von gemeinsam genutztem Speicher ein hoher Ressourcenbedarf. Auf jedem Prozessor muss eine eigenständige Instanz des Sigma0-Servers, die Zugriff auf den gesamten physischen Speicher hat, laufen. Um gemeinsam genutzten Speicher zu implementieren, wird pro Prozessor eine Task benötigt, welche prozessorlokal Zugriff auf den gemeinsam genutzten Speicher erhält. Die Tasks einer Anwendung müssen daher miteinander kooperieren, um gemeinsam genutzten Speicher zu realisieren.

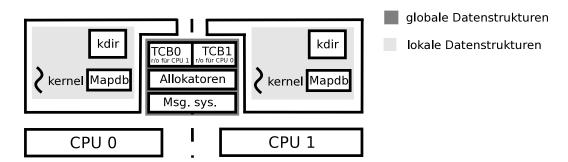

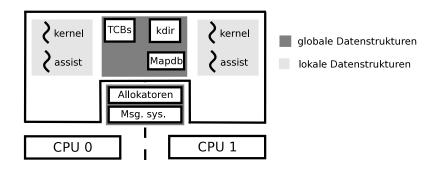

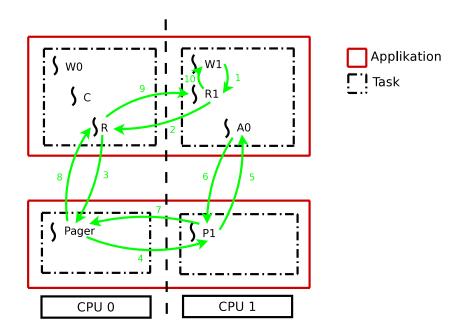

Abbildung 2.1: Schematische Darstellung des Kern-Modells der aktuellen Implementierung

Der Kern bietet keine Unterstützung, um Seiten, die von mehreren Tasks genutzt werden, all diesen Tasks zu entziehen. Eine Implementierung würde zu einer vergleichsweise hohen Komplexität führen, da die Seitentabellen der Tasks, die gemeinsam genutzten Speicher implementieren, als Cache einer übergeordneten Datenstruktur funktionieren. Deshalb müssen beim Entzug einer Seite auf jedem Prozessor die entsprechenden Einträge ungültig gemacht werden. Dafür sind zusätzliche Übergänge von der Kern- zur Benutzerebene nötig.

Das Fehlen von durch den Kern unterstützter Thread-Migration verhindert eine transparente Lastverteilung für Anwendungen.

$2\ Grundlagen\ und\ verwandte\ Arbeiten$

# 3 Analyse

Durch die Limitierungen (siehe Abschnitt 2.3.3) der aktuellen Implementierung wurden bislang die folgenden Probleme umgangen:

Mapping-Datenbank: Es gibt keine von mehreren Prozessoren gemeinsam genutzte Mapping-Datenbank. Jeder Prozessor verwaltet seine eigene Mapping-Datenbank. Konkurrierende Zugriffe auf die Mapping-Datenbank sind somit nicht möglich, da per Konstruktion keine Operationen erlaubt sind, die Modifikationen an mehr als einer Mapping-Datenbank erfordern.

**TLB-Konsistenz:** Der Kern muss nach Seitentabellenänderungen keine Konsistenz der TLBs über Prozessorgrenzen hinweg sicherstellen, da TLBs niemals Einträge von Seitentabellen von Tasks anderer Prozessoren enthalten können.

Migration: Transparente Thread-Migration ist mit dem aktuellen Modell nicht möglich. Es lassen sich auf Benutzerebene nur komplette Tasks transferieren, indem erst der Zustand der Task extrahiert, eine neue Task erzeugt und ihr der Zustand der zu transferierenden Task übertragen wird. Bei diesem Vorgang bleibt die Identität der Task nicht erhalten. Das muss von Anwendungen berücksichtigt werden.

Im folgenden beschreibe ich Weiterentwicklungen, mit denen die oben genannten Beschränkungen beseitigt werden sollen. Ich werde die Vor- und Nachteile diskutieren und sie hinsichtlich ihrer Eignung zum Erreichen der nachfolgend genannten Ziele untersuchen.

Für die Definition der Ziele, die mit der Weiterentwicklung von FIASCOMP erreicht werden sollen, gehe ich bei der Arbeitsbelastung des Systems von den folgenden zwei Annahmen aus:

- Anwendungen sind für den lokalen Fall optimiert und

- verwenden gemeinsam genutzten Speicher.

In [Völ02] beschreibt Völp einen Mechanismus, mit dem das Gesamtsystem partitioniert wird (Zuweisung von *Threads* auf Prozessoren). Es gibt einen Rückmeldemechanismus, der angibt, ob bestimmte Operationen eines *Threads* besonders häufig über Prozessorgrenzen hinweg erfolgen. In diesem Fall kann das Partitionierungsschema angepasst werden. Es wird zwischen dynamischer und statischer Partitionierung unterschieden. Die dynamische Partitionierung ermöglicht eine bessere Anpassung an sich ändernde Lastsituationen des Systems und ist für allgemeine Arbeitslasten daher besser geeignet.

Auf Lokalität optimierte Anwendungen sollen nicht durch einen langsameren Kernmechanismus für lokale Operationen verlangsamt werden. Mit der Weiterentwicklung sollen außerdem die in Abschnitt 2.3.3 genannten Limitierungen der bisherigen FIASCOMP-Implementierung beseitigt werden.

Ziele für die Weiterentwicklung sind daher:

- Verringerung des Ressourcen-Bedarfs durch:

- Vermeidung der Duplikation der Seitentabellen im Kern,

- Beseitigung der dedizierten Mapping-Datenbank für jeden Prozessor und

- Verringerung des Mehraufwands an Laufzeit

- Verzögern prozessorlokaler Operationen durch Cross-Prozessor-Synchronisation vermeiden und

- Erhaltung der Echtzeiteigenschaften von FIASCO.

Als Anwendungsszenario für das System nehme ich ein Multiserver-Betriebssystem und eine hypothetische Mehrprozessorvariante von L<sup>4</sup>Linux an.

In den folgenden Abschnitten werde ich einige Begriffe verwenden, die hier zur besseren Verständlichkeit zunächst definiert werden.

**Heimat-Prozessor:** Dieser Begriff bezieht sich auf eine Task und benennt den Prozessor, auf dem ihre Seitentabelle verwaltet wird. Üblicherweise ist das der Prozessor, auf dem die Task erzeugt worden ist.

**Heimat-Thread:** Ein Heimat-*Thread* ist ein Thread, der auf dem Heimat-Prozessor seiner Task ausgeführt wird.

**Fern-Thread:** Ein Fern-*Thread* wird auf einem anderen Prozessor als dem Heimat-Prozessor seiner Task ausgeführt.

In den folgenden Abschnitten werde ich drei Modelle vorstellen, nach denen der FIAS-COMP-Kern weiterentwickelt werden kann. Das erste Modell, Modell 1, ermöglicht es, einzelne *Threads* einer Task auf unterschiedlichen Prozessoren laufen zu lassen. Im Modell 2 implementiert der Kern einen gemeinsam genutzten Adressraum. Das Modell 3 bietet durch den Kern unterstützte *Thread*-Migration. Um die Unterscheidung der einzelnen Modelle zu erleichtern, werde ich im folgenden das bisherige Modell *Modell A* nennen. Danach folgt die Bewertung aller Modelle und die Implementierung eines Modells.

#### 3.1 Modell 1 - Cross-Prozessor-Tasks

Im bisherigen FIASCOMP-Modell sind Tasks und deren *Threads* auf einen Prozessor beschränkt. Dadurch kann eine Anwendung den Geschwindigkeitsgewinn durch die parallele Ausführung von unabhängigen *Threads* nicht für sich ausnutzen, ohne den Mehraufwand für die Erzeugung mehrerer Tasks aufzubringen.

Das Modell 1, welches ich in den folgenden Abschnitten vorstelle, ermöglicht es, einzelne *Threads* einer Task auch auf anderen Prozessoren auszuführen. Damit können Adressräume über Prozessorgrenzen hinweg genutzt werden. Es wird erwartet, dass die Anzahl der für eine bestimmte Last benötigten Tasks reduziert werden kann.

#### 3.1.1 Scheduling

Wie von Marcus Völp in [Völ02] beschrieben, sind die Laufzeitkosten für die Synchronisation einer globalen Ready-Liste sehr hoch. Der aktuelle FIASCO-MP-Kern verwendet prozessorlokales Scheduling. Prioritäten haben deshalb nur prozessorlokal eine Bedeutung, da *Threads* unterschiedlicher Prioritäten auf unterschiedlichen Prozessoren parallel laufen können. Die Strategie, Scheduling-Entscheidungen prozessorlokal zu treffen, wird, wie aus den im Kapitel 2 vorgestellten Arbeiten hervorgeht, häufig verwendet.

Um diese Laufzeitkosten zu vermeiden, wird das prozessorlokale Scheduling weiterhin bevorzugt. Fern-*Threads* werden den Scheduling-Entscheidungen des Prozessors, auf dem sie laufen, unterworfen.

#### 3.1.2 Speicherverwaltung

Der Translation Lookaside Buffer (TLB) ist ein Cache der übergeordneten Seitentabellen und speichert Adressübersetzungen. Mit der Nutzung von Adressräumen auf mehreren Prozessoren müssen TLBs unterschiedlicher Prozessoren mit der Seitentabelle der Task konsistent gehalten werden. Wird ein Eintrag aus der Seitentabelle gelöscht oder wird einer Task ein Mapping entzogen, dann müssen zugehörige TLB-Einträge in den TLBs aller betroffenen Prozessoren ungültig gemacht werden.

Die Uni-Prozessor-Implementierung der Unmap-Operation beinhaltet die TLB-Inva lidierung. Im Remote-Fall funktioniert dieser Mechanismus nicht mehr, da die Unmap-Operation nur auf einem Prozessor durchgeführt wird. Deshalb wird ein Konsistenzprotokoll für die TLBs aller Prozessoren benötigt. Die folgenden Abschnitte stellen zwei unterschiedliche Strategien vor, nach denen die TLBs aller Prozessoren konsistent gehalten werden können.

#### Eifrige TLB-Löschung

Bei diesem Ansatz werden die TLBs aller Prozessoren bei jeder Unmap-Operation gelöscht. Dazu wird eine Nachricht an alle Prozessoren verschickt, die daraufhin ihre TLBs löschen. Einen weiteren Ansatz, der die Nutzung der TLBs mit berücksichtigt, stelle ich im folgenden Abschnitt vor.

Dieser Ansatz hat große Auswirkungen auf die Gesamtgeschwindigkeit, da potentiell auch TLBs von Prozessoren gelöscht werden, auf denen keine Fern-*Threads* laufen. Der Einfluss auf die Gesamtgeschwindigkeit muss experimentell überprüft werden.

#### Selektive TLB-Löschung

Das Wissen darüber, welche Tasks von Änderungen eines Mappings betroffen sind, steckt in den Mapping-Bäumen selbst. Mit Hilfe dieses Wissens lässt sich der TLB gezielter löschen.

Zunächst wird an jeden Prozessor wiederum eine Nachricht zum Löschen des TLBs geschickt. Jeder Prozessor überprüft vor dem Löschen, ob gerade ein *Thread* einer betroffenen Task läuft und löscht ggf. den TLB.

Mit Hilfe einer globalen Kern-Datenstruktur könnte ermittelt werden, auf welchem Prozessor welche *Threads* laufen. Damit kann entschieden werden, welche Prozessoren von einer Unmap-Operation betroffen sind. Die Nachrichten brauchen nur noch an diese Prozessoren geschickt zu werden. So werden die Auswirkungen auf die betroffenen Prozessoren begrenzt.

In [Uhl05] wird mit der *Processor Cluster Mask* ein Verfahren beschrieben, mit dem sich die Zuordnung von Ressourcen zu Prozessoren effizient verwalten lässt. Dieses Verfahren kann auch hier verwendet werden.

#### 3.1.3 Prozessor-ID

Die Kernel-Info-Page (KIP) ist in L4 eine Datenstruktur, die Informationen über den Speicher, den Prozessor und die Kern-Schnittstelle enthält. Im bisherigen Modell konnte ein Thread sich die KIP einblenden lassen und daraus die Prozessor-ID auslesen. Fern-Threads haben in diesem Fall jedoch die KIP des Heimat-Prozessors eingeblendet und können daher nicht die korrekte Prozessor-ID ermitteln.

Als mögliche Lösung schlage ich einen neuen Systemruf vor, der die Prozessor-ID aus dem *Thread Control Block* (TCB) des jeweiligen *Threads* ausliest. Ebenfalls möglich ist die Erweiterung des 14\_myself-Systemrufs mit dem z.B. die *Thread*-ID ermittelt werden kann. Unterstützt der Kern *Userlevel Thread Control Blocks* (UTCBs), so kann man die Prozessor-ID in einem Feld des UTCBs speichern und der *Thread* kann sie dort auslesen.

#### 3.1.4 Kommunikation

Für Fern-*Threads* werden nur Short- und Long-IPC erlaubt. Fern-*Threads* können keine Speicher-Mappings annehmen oder verschicken, da jeder Prozessor weiterhin seine eigene Mapping-Datenbank für seine Tasks verwaltet. Die Mapping-Datenbanken unterschiedlicher Prozessoren werden nicht synchronisiert.

# 3.2 Modell 2 - Gemeinsam genutzte Mapping-Datenbank

In dem hier vorgestellten Modell (im Folgenden Modell 2) werden die bisher für jeden Prozessor dedizierten Mapping-Datenbanken durch eine einzige globale Mapping-Datenbank ersetzt. Dafür muss festgelegt werden, auf welchen Prozessoren Mappings

entgegengenommen werden dürfen bzw. wie der Zugriff auf die Mapping-Datenbank synchronisiert wird.

Es entfallen die begrenzenden Einschränkungen:

- Ressourcen-Vervielfältigung (Seitentabellen und Mapping-Datenbank) und

- keine Mappings über Prozessorgrenzen hinweg.

Für die Benutzerebene wird im Modell 2 durch den Kern ein gemeinsamer Adressraum auf allen Prozessoren zur Verfügung gestellt. Damit wird der Aufwand (Speicher und Laufzeit) für Anwendungen mit Cross-Prozessor-Adressräumen reduziert.

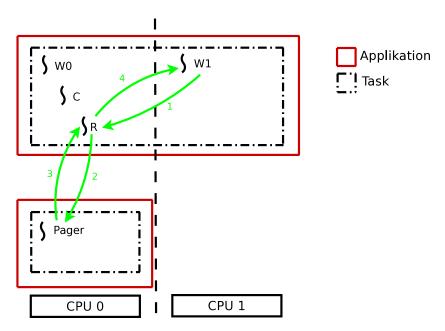

Abbildung 3.1: Schematische Darstellung des Kern-Modells von Modell 2

#### 3.2.1 Speicherverwaltung

Zugriffe auf gemeinsam genutzte Daten des Kerns, z.B. die Mapping-Datenbank, müssen synchronisiert werden, da der Zugriff parallel auf unterschiedlichen Prozessoren erfolgen kann.

#### Seitentabellen

Änderungen an Seitentabellen müssen sychronisiert werden. Dazu kann entweder die gesamte Seitentabelle durch ein Lock oder durch eine feiner granulare Variante geschützt werden. Bei der feingranularen Lösung wird zunächst die erste Ebene (Seitentabellenverzeichnis) durch ein Lock geschützt. Ist die entsprechende Seitentabelle (zweite Ebene) gefunden, wird diese ebenfalls gelockt. Anschließend kann das Lock des Seitentabellenverzeichnisses wieder freigegeben werden. Dieses Locking-Schema erhöht die Skalierbarkeit gegenüber der grobgranularen Lösung. Der Nachteil ist, dass diese Lösung aufwändiger zu implementieren ist.

#### **Allokatoren**

Tabelle 3.1: Allokatoren in FIASCO und deren Verwendung

| Allokator        | Verwendung                                                        |  |

|------------------|-------------------------------------------------------------------|--|

| slab_cache_anon  | einfacher Slab-Allokator                                          |  |

| Kmem_slab_simple | leitet von slab_cache_anon ab, Allokation von Speicher in Seiten- |  |

|                  | größe                                                             |  |

| Kmem_slab        | leitet von Kmem_slab_simple ab, Allokation von Speicher größer    |  |

|                  | als eine Seite, ein Allokator für jede Mapping-Baum-Größe, Task-  |  |

|                  | erzeugung, Erzeugung von Scheduling-Kontexten, Initialisierung    |  |

|                  | des Region-Managers, Allokation für FPU-Zustand                   |  |

| Mapped_allocator | Kmem_slab::block_alloc und Kmem_slab_simple::block_alloc          |  |

|                  | für Speicher kleiner als eine Seite, Physframe::alloc,            |  |

|                  | Vmem_alloc::init (für Zero-Page und page_alloc)                   |  |

| Kmem_alloc       | leitet von Mapped_allocator ab, Allokator für Kern-Speicher, Sei- |  |

|                  | tentabellenallokation in Space::v_insert, JDB                     |  |

| List_alloc       | Kmem_alloc::alloc                                                 |  |

| Vmem_alloc       | Initialisierung von UTCBs und der IDT, Kmem_slab::block_alloc     |  |

|                  | für Speicher größer als eine Seite, Initialisierung einer neuen   |  |

|                  | Task, Initialisierung des Kern-Threads                            |  |

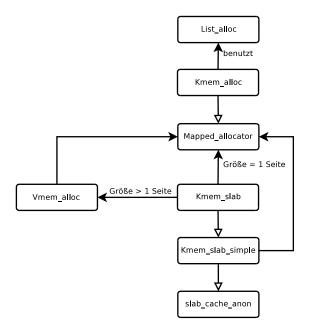

Die Allokatoren reservieren Speicher aus einem globalen Pool. Aus diesem Grund müssen Allokatoren, die parallel auf unterschiedlichen Prozessoren verwendet werden können, durch Locks vor wechselseitigem Zugriff geschützt werden. Im FIASCO-Kern werden die in Tabelle 3.1 beschriebenen Allokatoren verwendet. Aus dieser Tabelle geht hervor, dass alle Allokatoren parallel verwendet werden können, da sie z.B. für die Task-Erzeugung und Allokation von Speicher für Kern-Objekte benutzt werden. Deshalb müssen sie synchronisiert werden. In Abbildung 3.2 sind die Abhängigkeiten der in FIASCO verwendeten Allokatoren dargestellt.

#### Mapping-Datenbank

Mit der Implementierung eines gemeinsam genutzten Adressraums durch den Kern wird nur noch eine systemglobale Mapping-Datenbank benötigt. Da Mappings parallel auf unterschiedlichen Prozessoren etabliert werden können, muss die Mapping-Datenbank vor wechselseitigem Zugriff geschützt werden. Mapping-Hierarchien werden in der Mapping-Datenbank in Mapping-Bäumen gespeichert. In der aktuellen Implementierung werden zum Schutz der Mapping-Bäume Helping-Locks verwendet. Diese Helping-Locks können nicht mehr verwendet werden, da die implizite Annahme, dass bei Lock-Contention zum Lock-Halter umgeschaltet werden kann, nicht mehr für MP-Systeme gilt. Da Map- und Unmap-Operationen relativ lange Laufzeiten haben können, wird ein neuer, unterbrechbarer Locking-Mechanismus benötigt, um den Einfluss auf die Latenz von Echtzeitaufgaben zu minimieren.

Abbildung 3.2: Abhängigkeiten der in Fiasco verwendeten Allokatoren

Für die Allokation von Speicher für die Mapping-Bäume wird für jede Baumgröße ein spezifischer Slab-Allokator verwendet. Diese Allokatoren sind in einem Feld gespeichert.

# 3.3 Modell 3 - Thread-Migration

Im Modell A gibt es keine Möglichkeit, einzelne *Threads* für eine bessere Lastverteilung auf andere Prozessoren zu migrieren. Darin lassen sich nur komplette Tasks transferieren, wobei aber die Identität dieser Task nicht erhalten bleibt. Es gibt keine Unterstützung durch einen Kern-Mechanismus. Mit dem im Abschnitt 3.2 vorgestellten Modell 2 ist Thread-Migration von der Nutzerebene aus möglich. Allerdings ist dieser Vorgang aufgrund der zwischenzeitlichen Nicht-Existenz dieses *Threads* für die Außenwelt sichtbar, denn der Migrationsvorgang ist nicht atomar und kann daher unterbrochen werden.

Die Task-Migration im Modell A setzt sich aus insgesamt fünf Schritten zusammen und wird vollständig auf der Benutzerebene ausgeführt:

**Einfrieren:** Alle *Threads* der zu migrierenden Task werden angehalten und der Zustand wird, damit er sich nicht mehr ändert, in einem Schnappschuss festgehalten.

**Extrahieren:** Der die Migration durchführende *Thread* extrahiert den Zustand jedes *Threads* der zu migrierenden Task.

**Transferieren:** Auf dem Ziel-Prozessor wird eine neue Task mit der entsprechend benötigten Anzahl an *Threads* angelegt. Die *Threads* sind noch nicht lauffähig, da ihnen noch nicht der Zustand der zu transferierenden *Threads* übertragen wurde.

**Injizieren:** Der extrahierte Zustand jedes *Threads* wird auf einen der neu erzeugten *Threads* übertragen.

**Auftauen:** Die *Threads* der migrierten Task werden auf dem Ziel-Prozessor aufgeweckt und können dann dort ausgeführt werden. Anschließend müssen mögliche Kommunikationspartner benachrichtigt werden, da sich die Identität der *Threads* geändert hat.

Die Thread-Migration im Modell 2 läuft ähnlich ab.

Dieser komplexe Vorgang eignet sich nicht für dynamische Lastverteilung zwischen einzelnen Prozessoren. Diese Art der Migration ist nicht identitätserhaltend und damit für Kommunikationspartner sichtbar. Außerdem werden kooperierende Tasks auf unterschiedlichen Prozessoren benötigt, die die Migration durchführen.

Um diese Mängel zu beseitigen, stelle ich im nächsten Abschnitt ein weiteres Modell vor.

#### 3.3.1 Migration

Für *Thread*-Migration wird ein Kern-Mechanismus benötigt, der transparent bezüglich der Interaktion (IPC) zwischen *Threads* ist. Es ergeben sich Probleme mit: zwischenzeitlicher Migration, nicht abgeschlossenen Nachrichten und dem Locking von *Threads*.

Um Verklemmungssituationen zu vermeiden, muss verhindert werden, dass sich zwei *Threads* gegenseitig migrieren wollen. Deshalb dürfen *Threads* nur von einem dedizierten *Thread* migriert werden. Der Migrations-*Thread* übernimmt in diesem System die Lastverteilung. Der Migrations-*Thread* kann ein zusätzlicher Kern-*Thread* oder ein Server-*Thread* auf Benutzerebene sein.

#### 3.3.2 Kommunikation

Threads müssen um eine Warteschlange für ausstehende Operationen und Nachrichten erweitert werden. Das ist nötig, da während der Migration Nachrichten an den zu migrierenden Thread eintreffen können. Damit keine Nachrichten verloren gehen, muss der Kern solche Nachrichten in einem Puffer zwischenspeichern und nach der Migration zustellen. Wird ein Thread gerade migriert, so muss sichergestellt werden, dass die Bearbeitung jeder Nachricht nicht beliebig verzögert wird.

#### 3.4 Diskussion

In diesem Abschnitt fasse ich zunächst noch einmal die Eigenschaften der drei von mir vorgestellten Modelle zusammen. Anschließend diskutiere ich Vor- und Nachteile der jeweiligen Modelle.

#### 3.4.1 Modelleigenschaften

Das im Abschnitt 3.1 vorgestellte Modell 1 ermöglicht die Ausführung von *Threads* einer Task auf unterschiedlichen Prozessoren. Die sog. Fern-*Threads* dürfen Seitenfehler auslösen und *Short*- und *Long*-IPC-Nachrichten verschicken. Das Verschicken von Speicher-Mappings von und an Fern-*Threads* ist nicht erlaubt.

Im Modell 2 werden die bislang dediziert für jeden Prozessor vorhandenen Mapping-Datenbanken durch eine systemglobale ersetzt. Die Duplikation der Seitentabellen entfällt, da vom Kern ein gemeinsamer Adressraum auf allen Prozessoren zur Verfügung gestellt wird.

Im Modell 3 wird ein für Anwendungen teilweise transparentes Multiprozessorsystem geschaffen. Multi-Thread-Anwendungen ohne Wissen über die Multiprozessorhardware können aufgrund der Unterstützung durch den Kern trotzdem den Vorteil aus paralleler Ausführung einzelner *Threads* ziehen, da der Kern oder ein Server auf Benutzerebene *Threads* dynamisch auf unterschiedliche Prozessoren verteilen kann. Die Management-Komponenten müssen jedoch die Zuordnung von *Threads* zu Prozessoren kennen. Deshalb kann man hier nur von einem teilweise transparenten Modell sprechen.

#### 3.4.2 Vor- und Nachteile

Aufgrund der Beschränkung von Fern-Threads auf Short-IPC im Modell 1 sind keine Speicher-Mappings über Prozessorgrenzen hinweg möglich. Die Anordnung von Threads auf den Prozessoren kann sich kritisch auf die Gesamtgeschwindigkeit des Systems auswirken, da bei ungünstiger Anordnung zahlreiche Nachrichten an den Heimat-Prozessor notwendig werden können. Der Heimat-Prozessor stellt einen potentiellen Flaschenhals dar, da er den gesamten Verwaltungsaufwand für die Seitentabellen und die Mapping-Datenbank seiner Tasks zu tragen hat.

Die im Abschnitt 3 genannten Ziele lassen sich mit dem Modell 1 nicht erreichen. Jedoch werden wichtige Grundlagen (z.B. TLB-Invalidierungen und Cross-Prozessor-Tasks) gelegt, die für das Modell 2 benötigt werden.

Im Modell 2 wird der Ressourcen-Verbrauch (Speicher) des Kerns gesenkt. Es wird erwartet, dass die für eine bestimmte Last benötigte Anzahl von Tasks reduziert wird, da z.B. der Kern bereits einen gemeinsam genutzten Adressraum implementiert. Außerdem entfällt der Laufzeitmehraufwand für die Erzeugung mehrerer Tasks, um gemeinsam genutzten Speicher auf Nutzerebene zu konstruieren.

Die Vorteile (geringerer Ressourcenverbrauch und weniger Laufzeitaufwand) werden durch ein komplexeres Kern-Modell erzielt. Um Fortschritt von *Threads* bei langen kritischen Abschnitten auch über Prozessorgrenzen hinweg erzielen zu können, wird ein komplexer Synchronisationsmechanismus für die Mapping-Datenbank benötigt. Ein einfaches Spin-Lock zum Schutz der Mapping-Datenbank erfüllt zwar die Fairness-Eigenschaft, da der kritische Abschnitt aber nicht unterbrechbar ist, hat es negative Auswirkungen auf die Echtzeiteigenschaften. Das lässt sich mit einem unterbrechbaren Spin-Lock verhindern. Ein unterbrechbares Spin-Lock kann jedoch zu unbegrenzter Verzögerung von Operationen einzelner *Threads* führen. Deshalb wird ein unterbrechbarer und fairer

Lock-Mechanismus benötigt, der das Verhungern von *Threads* verhindert.

Das Kern-Modell von Modell 3 ist das komplexeste der drei vorgestellten Modelle. Die Auswirkungen davon auf das Echtzeitverhalten von FIASCO sind unklar. Es ist am besten für eine allgemeine Arbeitslast eines MP-Systems geeignet, aber für das von mir angenommene Anwendungsszenario (L<sup>4</sup>Linux) nicht nötig, da Linux selbst eine Lastverteilung implementiert.

#### 3.4.3 Schlussfolgerung

Aus der Diskussion in Abschnitt 3.4 geht hervor, dass das in Abschnitt 3.1 vorgestellte Modell 1 mit Cross-Prozessor-Tasks bereits die für eine bestimmte Arbeitslast benötigte Taskmenge reduzieren kann. Dieses System ist dafür geeignet, mehrere L<sup>4</sup>Linux-Uniprozessorinstanzen parallel auf unterschiedlichen Prozessoren auszuführen. Für die Ausführung einer hypothetischen L<sup>4</sup>Linux-MP-Variante ist es weniger geeignet, da nach wie vor ein hoher Ressourcenverbrauch durch die duplizierten Kern-Datenstrukturen benötigt wird.

Der hohe Ressourcenverbrauch wird im zweiten Modell beseitigt. Durch die Implementierung eines gemeinsam genutzten Adressraums im Kern entfällt die Duplikation von Kern-Datenstrukturen. Das Modell 2 vereinfacht die Konstruktion eines L<sup>4</sup>Linux-MP-Systems, da Linux-SMP selbst auch einen gemeinsam genutzten Adressraum für Anwendungsprogramme implementiert.

Das Modell 3 mit durch den Kern unterstützter *Thread*-Migration bietet für die Umsetzung von L<sup>4</sup>Linux-MP keine zusätzlichen Vorteile. Linux implementiert selbst weitere SMP-Mechanismen wie z.B. Lastverteilung. Daher wird die Funktionalität von Modell 3 für L<sup>4</sup>Linux-MP nicht benötigt.

Ich werde deshalb im Rahmen dieser Arbeit das Modell 2 mit einem gemeinsam genutzten Adressraum implementieren. Es bietet die Eigenschaften, die zum Erreichen der im Abschnitt 3 genannten Ziele

- Verringerung des Ressourcen-Bedarfs,

- Verhinderung von langsamen prozessorlokalen Operationen durch Cross-Prozessor-Synchronisation und

- Erhaltung der Echtzeiteigenschaften von Fiasco

nötig sind. Es ist für die angenommene Arbeitslast geeignet.

# 4 Design

In diesem Kapitel stelle ich den Entwurf für die Weiterentwicklungen von FIASCOMP vor. Im vorangegangenen Kapitel habe ich mich für die Implementierung des Modells 2 entschieden. Der zentrale Punkt dieses Modells ist die system-globale Mapping-Datenbank. Um bei konkurrierenden Zugriffen von unterschiedlichen Prozessoren auf die Mapping-Datenbank die Echtzeitfähigkeiten zu erhalten, wird ein unterbrechbarer Locking-Mechanismus über Prozessorgrenzen hinweg benötigt. Deshalb bildet der Algorithmus für das Cross-Prozessor-Helping den Schwerpunkt dieses Kapitels.

#### 4.1 Thread-Interaction

#### 4.1.1 IPC

Der Cross-Prozessor-IPC-Pfad ist mit dem lokalen IPC-Pfad integriert. Damit ist sichergestellt, dass der atomare Übergang zwischen dem Sende- und dem Empfangsteil einer Nachricht auch im Cross-Prozessorfall gewährleistet ist.

Um Adressräume über Prozessorgrenzen hinweg zu nutzen, wird *Pagefault-*IPC über Prozessorgrenzen erlaubt.

Um die Komplexität des Kerns zu begrenzen, ist es ein akzeptabler Kompromiss, dass der Cross-Prozessor-IPC-Pfad nur Register-Short-IPC implementiert. Der Einfluss von Cross-Prozessor-IPC auf die lokale IPC soll so klein wie möglich sein.

# 4.1.2 Remote-Ex-Regs

Über den Ex-Regs-Systemruf kann durch *Threads* der Zustand von anderen *Threads* verändert werden. Dazu wird das *Thread*-Lock des betroffenen *Threads* gegriffen und anschließend wird der *Thread* als nicht lauffähig markiert. Im Multiprozessorfall kann es zu einem Deadlock kommen, wenn zwei *Threads* auf unterschiedlichen Prozessoren sich gegenseitig mit dem Ex-Regs-Systemruf manipulieren.

Mit Hilfe des Message-Box-Systems und dessen Ausführung im Kontext eines zusätzlichen Kern-*Threads* wird eine Blockierung vermieden. Die Bearbeitung des Ex-Regs-Aufrufs erfolgt im Kontext dieses Kern-*Threads*.

#### 4.1.3 Nachrichtenrate

Die Rate, mit der ein Prozessor Nachrichten an andere Prozessoren schickt, muss begrenzt werden. Damit wird sichergestellt, dass auf dem Empfänger-Prozessor in den Sendepausen *Threads* laufen können.

Die Rate, mit der Nachrichten verschickt werden, ist ein anpassbares Kriterium und hängt stark von der Arbeitslast des Systems ab. Es ist sinnvoll, diese empirisch durch Messung zu ermitteln.

# 4.2 Synchronisation der Mapping-Datenbank

In diesem Abschnitt beschreibe ich, wie im Modell 2 Zugriffe auf die Mapping-Datenbank synchronisiert werden, damit die Auswirkungen auf das Zeitverhalten begrenzt werden können. In vielen Modellen werden Ressourcen an Prozessoren gebunden [Liu00]. Zusätzlich wird die Annahme gemacht, dass die Ressourcennutzungszeit begrenzt ist. Beide Annahmen sind schlecht mit den Charakteristiken der Mapping-Datenbank vereinbar. Mapping-Operationen können Echtzeit-Operationen zwar nicht behindern, können aber nicht Bestandteil von Echtzeitaufgaben sein, da die maximale Ausführungszeit nicht begrenzt ist (abhängig von der Mapping-Baum-Größe). Die Mapping-Datenbank an einen Prozessor zu binden, würde diesen Prozessor potentiell zu einem Flaschenhals machen.

Jeder einzelne Prozessor kann zu jedem Zeitpunkt nur einen Ausführungspfad bearbeiten. Durch Zeitmultiplex mehrerer Codepfade auf einem Prozessor wird innerhalb eines bestimmten Zeitrahmens das Weiterlaufen des Gesamtsystems erreicht. Bestimmte Codepfade dürfen nicht parallel laufen (kritische Abschnitte), da sie auf gemeinsame Daten zugreifen. Solche Abschnitte müssen mit Mechanismen geschützt werden, die eine exklusive Abarbeitung der kritischen Abschnitte sicherstellen. Eine Möglichkeit dafür sind Locks.

Für die Nutzung der durch ein Lock geschützten Ressource muss zunächst das Lock gesetzt werden. Ist das Lock bereits belegt, blockieren *Threads* beim Zugriff darauf. Durch diese Konstruktion kann es im System zum Problem der Prioritätsumkehr kommen, was den Fortschritt von lauffähigen *Threads* verhindert. FIASCO vermeidet Prioritätsumkehr durch Helping-Locks.

Ein an einem besetzten Lock blockierter *Thread* kann, um seine eigene Blockierzeit zu minimieren, zu dem Lock-Halter umschalten und so die Ausführung des kritischen Abschnitts fortsetzen. Damit wird erreicht, dass der Lock-Halter das Lock möglichst schnell wieder freigibt. Auf Einprozessorsystemen ist das problemlos möglich, da die unterschiedlichen Codepfade durch Zeitmultiplex serialisiert werden. Bei MP-Systemen treten dabei folgende Probleme auf:

- Ausführung des kritischen Abschnitts zu jedem Zeitpunkt nur auf einem Prozessor sicherstellen und

- mehrere gleichzeitig zum Helfen bereite Helfer.

Diese Probleme werden durch Synchronisation zwischen Besitzern und Helfern sowie zwischen Helfern untereinander gelöst.

Für die Synchronisation sind unterschiedliche Implementierungen möglich. Das angestrebte Ziel ist es, die bestehenden Codepfade möglichst wenig zu verändern. Die

Synchronisation zwischen Besitzer und dem ersten Helfer erfolgt durch die Unterbrechung des Besitzers durch den ersten Helfer mit Hilfe eines Disable-Requests. Solange es lauffähige Helfer gibt, führt der Besitzer den kritischen Abschnitt nicht auf seiner eigenen Zeitscheibe aus: der Helfer führt den kritischen Abschnitt auf seiner Zeitscheibe aus. Die Synchronisation zwischen einzelnen Helfern erfolgt über eine lockspezifische Helferliste, in die sich jeder Helfer einträgt. Mit Hilfe dieser Liste wird das Helfen serialisiert. Threads, die sich in dieser Liste befinden, werden aus der Ready-Liste ausgetragen. Damit können sie nicht vom Scheduler auf ihrem Prozessor ausgewählt werden. Helfer warten auf die Benachrichtigung, mit dem Helfen beginnen zu können. Nach dem Eintreffen einer Benachrichtigung, mit dem Helfen zu beginnen, wird die Ausführung fortgesetzt.

Eine andere Möglichkeit der Synchronisation wäre, dass potentielle Helfer permanent den Zustand des Besitzers überprüfen (Polling) und bei Unterbrechung desselben mit dem Helfen beginnen. Während des ständigen Abfragens verstreicht die Prozessorzeit ungenutzt. Aufgrund der zusätzlichen Instruktionen und der aufwändigen atomaren Operationen wird der switch\_to-Pfad langsam.

#### 4.2.1 Algorithmus

Bei der Lockanforderung wird überprüft, ob das Lock bereits besetzt ist. Ist das Lock bereits besetzt, wird der *Thread* in die Anwärterliste und die Helferliste eingetragen. Ist der Helfer der erste Helfer, d.h. es gibt keine weiteren lauffähigen Helfer und der Besitzer führt den kritischen Abschnitt auf seiner eigenen Zeitscheibe aus, unterbricht der Helfer den Besitzer. Anschließend führt der Helfer den Besitzer auf seiner Zeitscheibe aus.

Wird ein Helfer bei der Ausführung des kritischen Abschnitts unterbrochen, wird überprüft, ob weitere Helfer in der Helferliste eingetragen sind. Ist dies der Fall, müssen zwei Fälle unterschieden werden.

- 1. Der nächste Helfer führt auf demselben Prozessor wie der unterbrochene Helfer aus. Der unterbrochene Helfer wird in die lokale Ready-Liste eingetragen. Ein direktes Umschalten ist nicht möglich, da so das lokale Scheduling ignoriert werden würde. Alle nachfolgenden Helfer, die lokal sind, werden ebenfalls in die Ready-Liste eingefügt, da nicht bekannt ist, ob sie lokal die höchste Priorität haben und damit lauffähig sind.

- 2. Der nächste Helfer führt auf einem anderen Prozessor als der unterbrochene Helfer aus. Der neue Helfer wird benachrichtigt, dass er mit dem Helfen beginnen kann.

Erhält ein potentieller Helfer die Nachricht, mit dem Helfen beginnen zu können, muss überprüft werden, ob der Helfer überhaupt noch lauffähig ist. Während seiner Wartezeit kann seine Lauffähigkeit z.B. durch einen höher priorisierten *Thread* verändert worden sein. Im lokalen Fall wird der Helfer in die Ready-Liste eingetragen und ein Schedule durchgeführt. Im *Remote*-Fall wird die Priorität des Helfers mit der Priorität des aktuell auf dem Prozessor laufenden *Threads* verglichen. Deswegen ist das Scheduling einfacher, als eine Erweiterung der Scheduling-Schnittstelle, um die höchste Priorität ermitteln zu

können. Hat der Helfer die höchste Priorität, wird durch switch\_to auf dem Prozessor des Helfers zu ihm umgeschaltet. Andernfalls wird sofort der nächste Helfer aus der Helferliste benachrichtigt.

Mit dem vorgestellten Mechanismus wird Fortschritt garantiert und die Ausführung des kritischen Abschnitts auf jedem Prozessor ermöglicht. Der kritische Abschnitt wird jedoch zu jedem Zeitpunkt auf höchstens einem Prozessor ausgeführt.

Der Helping-Vorgang wird durch eine implizite Migration des Besitzer-Kontexts für maximal die Dauer des kritischen Abschnitts durchgeführt. Der Helfer führt den Besitzer-Kontext auf seiner Zeitscheibe lokal auf seinem Prozessor aus. Die Migration erfolgt höchstens für die Dauer der Ressourcennutzung und beinhaltet keine Migration auf Benutzerebene.

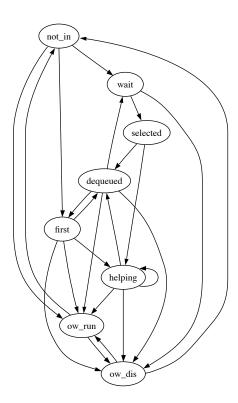

Während des Helping-Vorgangs nehmen der Besitzer und die Helfer unterschiedliche Zustände an. Diese sind in dem folgenden Zustandsübergangsdiagramm (Abbildung 4.1) dargestellt. In Tabelle 4.1 sind die einzelnen Zustände beschrieben.

Abbildung 4.1: Zustandsübergangsdiagramm für Zustände, die Besitzer und Helfer einnehmen können

Tabelle 4.1: Beschreibung der Zustände des Zustandsgraphen

| Name     | Beschreibung                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------|

| not_in   | Zustand not involved. Alle Threads, die weder das Recht zur exklusiven                              |

|          | Nutzung der Ressource besitzen, noch die Ressource anfordern.                                       |

| ow_run   | Zustand owner running. Der Thread besitzt das Recht zur exklusiven                                  |

|          | Nutzung der Ressource. Der Besitzer ist in der lokalen Ready-Liste und                              |

|          | arbeitet den kritischen Abschnitt selbst ab oder er wurde durch einen                               |

|          | höher priorisierten <i>Thread</i> unterbrochen.                                                     |

| ow_dis   | Zustand owner disabled. Der Thread besitzt das Recht zur exklusiven                                 |

|          | Nutzung der Ressource. Der Besitzer wurde durch einen Helfer deakti-                                |

|          | viert. Der Helfer führt den kritischen Abschnitt aus (aktives Helfen).                              |

| wait     | Zustand waiting. Die Ressource wurde angefordert, aber das Recht noch                               |

|          | nicht zugeteilt. Ein anderer Helfer hilft momentan. Der Helfer befindet                             |

|          | sich in der Helferliste und wartet auf eine Benachrichtigung, mit dem                               |

|          | Helfen zu beginnen. Er befindet sich nicht mehr in der Ready-Liste und                              |

|          | kann damit vom Scheduler nicht ausgewählt werden.                                                   |

| first    | Zustand first. Die Ressource wurde angefordert, aber das Recht noch                                 |

|          | nicht zugeteilt. Der Helfer ist an erster Stelle in der Helferliste und wartet                      |

|          | auf den erfolgreichen Abschluss der Deaktivierung des Besitzers. Zum                                |

|          | Zeitpunkt des Eintreffen des Helfers gab es noch keine weiteren Helfer.                             |

| selected | Zustand selected. Die Ressource wurde angefordert, aber das Recht noch                              |

|          | nicht zugeteilt. Dieser Zustand ist ein Zwischenzustand. Der Helfer ist                             |

|          | an erster Stelle in der Helferliste und eine Benachrichtigung, mit dem                              |

|          | Helfen zu beginnen, ist unterwegs. Der Besitzer wurde bereits von einem anderen Helfer deaktiviert. |

| helping  | Zustand <i>helping</i> . Die Ressource wurde angefordert, aber das Recht noch                       |

| neiping  | nicht zugeteilt. Der Helfer ist erster in der Helferliste. Der Besitzer führt                       |

|          | den kritischen Abschnitt auf dem Prozessor des Helfers und dessen Zeit-                             |

|          | scheibe aus.                                                                                        |

| dequeued | Zustand dequeued. Die Ressource wurde angefordert, aber das Recht noch                              |

| acqueucu | nicht zugeteilt. Der Helfer wurde von einem lokalen <i>Thread</i> verdrängt.                        |

|          | Er wurde aus der Helferliste entfernt und in die Ready-Liste eingefügt.                             |

|          | Sobald er vom Scheduler erneut ausgewählt wird, reiht er sich wieder in                             |

|          | die Helferliste ein.                                                                                |

|          |                                                                                                     |

#### Parallele Aktivitäten

Beim MP-fähigen Helping-Mechanismus gibt es einige Aktivitäten, deren strikte Serialisierung, z.B. durch ein Spin-Lock im switch\_to-Pfad, zu Leistungseinbußen führen würde. Die Serialisierung würde die Skalierbarkeit verschlechtern. Deshalb wird an bestimmten Punkten ein gewisser Grad an Unbestimmtheit erlaubt und im Bedarfsfall wird mit Hilfe

eines serialisierenden Ereignisses ein bestimmter Zustand herbeigeführt.

- Übergang des Besitzers von ow\_run nach not\_in und parallel Übergang eines Helfers von first nach helping (Serialisierung durch Nachricht).

- Übergang mehrerer Threads von not\_in nach wait (Serialisierung durch Lock).

- Übergang mehrerer Threads von dequeued nach wait (Serialisierung durch Lock).

#### Invarianten

Bei der Konstruktion des Algorithmus habe ich mehrere Invarianten festgelegt, deren Verletzung das Nichterreichen der gesetzten Ziele zur Folge hätte:

- 1. Höchstens ein *Thread* führt zu jedem Zeitpunkt den kritischen Abschnitt aus (Korrektheit).

- 2. Wenn es mindestens einen Helfer gibt, existiert auch ein Besitzer.

- 3. Wenn sowohl Besitzer als auch Helfer ausführungsbereit sind, haben Helfer Vorrang und führen den kritischen Abschnitt aus. Damit werden Änderungen am switch\_to-Pfad vermieden, da potentielle Helfer nicht den Zustand des Besitzers abfragen und entsprechend handeln müssen.

- 4. Der kritische Abschnitt wird ausgeführt, wenn mindestens ein Anforderer des Locks lauffähig ist.

- 5. Der erste *Thread* in der Helferliste ist im Zustand first, selected oder helping. Alle weiteren *Threads* in der Helferliste befinden sich im Zustand wait. Wenn ein *Thread* im Zustand wait ist, dann gibt es auch einen *Thread* im Zustand first, selected oder helping.

- 6. Der Besitzer befindet sich nicht in der Helferliste. Damit wird die Weitergabe des Helfens vereinfacht. Die Ausführung des kritischen Abschnitts kann so an den nächsten *Thread* in der Helferliste weitergegeben werden kann.

#### Gekoppelte Übergänge

Der Zustandsübergang eines *Threads* im MP-Helping-Mechanismus kann möglicherweise zur Verletzung einer Invariante führen. Zur Aufrechterhaltung der Invarianten kann es daher nötig sein, den Zustand anderer *Threads* zu verändern. Die Tabellen 4.2 bis 4.7 listen alle relevanten Zustandsübergänge auf und zählen die Bedingungen, die für ihren Eintritt nötig sind, auf.

#### 4.2.2 Ablaufszenarien

Beim Ablauf des Multiprozessor-Helpings gibt es unterschiedliche Szenarien. Im Folgenden sind typische Abläufe dargestellt.

- 1. Das Lock wird freigegeben. Während dessen greift ein neuer *Thread* auf die Ressource zu. Der *Disable-Request* schlägt fehl (Meldung: neuer Besitzer, Freigeben des Locks und Einreihen in die Helferliste sind synchronisiert). Der neue *Thread* wird neuer Besitzer.

- 2. Ein Helfer beendet den kritischen Abschnitt. Dabei können die folgenden zwei Fälle auftreten:

- a) Ein anfordernder *Thread*, der auch Helfer sein kann, wird neuer Besitzer. Der neue Besitzer geht in den Zustand ow\_dis über und der aktuelle Helfer setzt das Helfen für den neuen Besitzer fort.

- b) Der Helfer wird selbst neuer Besitzer.

- i. Es gibt keine weiteren Helfer. Der neue Besitzer setzt die Ausführung unmittelbar fort (Zustand ow\_run).

- ii. Es gibt weitere Helfer in der Helferliste. Der neue Besitzer deaktiviert sich und benachrichtigt anschließend den nächsten Helfer.

- 3. Der letzte Helfer wird verdrängt. Die Helferliste ist leer. Der Besitzer wird aktiviert und in die *Ready*-Liste seines Prozessors eingereiht. Der Scheduler kann den Besitzer zur Ausführung auswählen.

Tabelle 4.2: Zustandsübergänge ausgehend vom Zustand not\_in

| Ereignis         | Bedingung            | Folgezustand | Beschreibung            |

|------------------|----------------------|--------------|-------------------------|

| Zugriff auf Res- | Ressource nicht be-  | ow_run       | Thread wird Besitzer    |

| source           | legt                 |              |                         |

| Zugriff auf Res- | Ressource belegt,    | wait         | Thread in Helferliste   |

| source           | andere Threads       |              | einreihen               |

|                  | versuchen bereits zu |              |                         |

|                  | helfen               |              |                         |

| Zugriff auf Res- | Ressource belegt,    | first        | Thread ist erster Hel-  |

| source           | Helferliste leer     |              | fer, Zustand des Besit- |

|                  |                      |              | zers nicht bekannt, da- |

|                  |                      |              | her Deaktivierung des   |

|                  |                      |              | Besitzers               |

Der Zustandsübergang  $not\_in \mapsto first$  hat bei einem aktuell ausführenden Besitzer den Übergang  $ow\_run \mapsto ow\_dis$  zur Folge. Der Helfer geht dann von first nach helping über.

Tabelle 4.3: Zustandsübergänge ausgehend vom Zustand  $\boldsymbol{wait}$

| Ereignis       | Bedingung | Folgezustand | Beschreibung             |

|----------------|-----------|--------------|--------------------------|

| Lock-Freigabe  |           | ow_dis       | Helfer ist erster in der |

| des vorherigen |           |              | Warte-Liste, weitere be- |

| Besitzers      |           |              | reite Helfer existieren  |

Tabelle 4.9: Zustandsübergänge ausgehend vom Zustand  $\emph{first}$

| Ereignis          | Bedingung               | Folgezustand | Beschreibung              |

|-------------------|-------------------------|--------------|---------------------------|

| disable-Request   |                         | helping      | Besitzer deaktiviert      |

| erfolgreich abge- |                         |              |                           |

| schlossen         |                         |              |                           |

| disable-Request   | Helfer ist Erster in    | ow_run       | Helfer ist neuer Besitzer |

| schlägt fehl,     | der Warte-Liste und     |              |                           |

| Lock-Freigabe     | Helferliste ist leer    |              |                           |

| durch Besitzer    |                         |              |                           |

| vor Deaktivierung |                         |              |                           |

| disable-Request   | Helfer ist Erster in    | ow_dis       | Helfer ist neuer Besitzer |

| schlägt fehl,     | der Warte-Liste, Hel-   |              |                           |

| Lock-Freigabe     | ferliste nicht leer     |              |                           |

| durch Besitzer    |                         |              |                           |

| vor Deaktivierung |                         |              |                           |

| disable-Request   | Helfer ist nicht Ers-   | helping      | der neue Besitzer wird    |

| schlägt fehl,     | ter in der Warte-       |              | deaktiviert               |

| Lock-Freigabe     | Liste                   |              |                           |

| durch Besitzer    |                         |              |                           |

| vor Deaktivierung |                         |              |                           |

| disable-Request   | Helfer ist Erster in    | dequeued     | während des Abschl-       |

| schlägt fehl,     | der Warte-Liste, Hel-   |              | usses der Unterbre-       |

| Lock-Freigabe     | ferliste ist leer, Hel- |              | chungsnachricht, wählt    |

| durch Besitzer    | fer hat lokal nicht die |              | der lokale Scheduler      |

| vor Deaktivierung | höchste Priorität       |              | einen höher priorisier-   |

|                   |                         |              | ten Thread aus            |

Der Zustandsübergang  $first \mapsto helping$  führt beim neuen Besitzer zum Übergang  $wait \mapsto ow\_dis$  oder  $dequeued \mapsto ow\_dis$ .

Tabelle 4.4: Zustandsübergänge ausgehend vom Zustand helping

| Ereignis        | Bedingung                  | Folgezustand | Beschreibung         |

|-----------------|----------------------------|--------------|----------------------|

| Lock-Freigabe   | Erster in Warte-Liste,     | ow_run       | Helfer ist neuer Be- |

| durch Helfer    | Helferliste leer           |              | sitzer               |

| Lock-Freigabe   | Erster in Warte-Liste,     | ow_dis       | Helfer ist neuer Be- |

| durch Helfer    | Helferliste nicht leer     |              | sitzer               |